# SystemVerilog 验证

# 测试平台编写指南

(原书第二版)

〔美〕克里斯・斯皮尔 著 张 春 麦宋平 赵益新 译

> 斜 学 出 版 社 北京

# ----- 目 录

| 第 | 1 | 章     | 金证 見    | 论    |             |       | <br> | <br> | ••• |

|---|---|-------|---------|------|-------------|-------|------|------|-----|

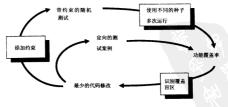

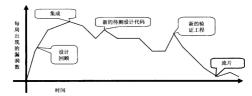

|   |   | 1.1   | 验证      | 花程   |             |       | <br> | <br> | :   |

|   |   |       |         |      |             |       |      |      |     |

|   |   | 1     |         |      |             |       |      |      |     |

|   |   | 1.2   |         |      |             |       |      |      |     |

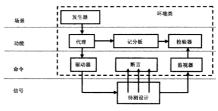

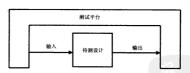

|   |   | 1.3   | 基本社     | 测试平台 | 的功能·        |       | <br> | <br> |     |

|   |   | 1.4   | 定向      | 削试   |             |       | <br> | <br> |     |

|   |   | 1.5   |         |      |             |       |      |      |     |

|   |   | 1.6   | 受约!     | 收的随机 | 激励 …        |       | <br> | <br> |     |

|   |   | 1.7   | 你的      | 直机化对 | 象是什么        | ζ     | <br> | <br> |     |

|   |   | 1     | . 7, 1  | 设备和工 | <b>「境配置</b> |       | <br> | <br> | ••• |

|   |   | 1     | .7.2    | 输入数1 | š           |       | <br> | <br> |     |

|   |   | 1     | . 7. 3  | 协议异为 | 5、错误手       | 口造例 … | <br> | <br> |     |

|   |   | 1     | . 7. 4  | 时延和日 | 1步          |       | <br> | <br> |     |

|   |   |       | . 7. 5  |      |             |       |      |      |     |

|   |   |       |         |      |             |       |      |      |     |

|   |   |       |         |      |             |       |      |      |     |

|   |   | 1.9   |         |      |             |       |      |      |     |

|   |   |       |         |      |             |       |      |      |     |

|   |   |       | . 10. 1 |      |             |       |      |      |     |

|   |   |       | . 10. 2 |      |             |       |      |      |     |

|   |   |       | . 10. 3 |      |             |       |      |      |     |

|   |   |       | . 10. 4 |      |             |       |      |      |     |

|   |   |       | . 10. 5 |      |             |       |      |      |     |

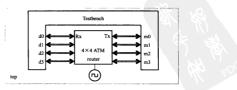

|   |   | 1.11  | 建.9     | 一个分月 | 長的側试        | 平台    | <br> | <br> | ]   |

|   |   |       | . 11. 1 | 创建一  | 个简单的        | 有驱动器  | <br> | <br> | ]   |

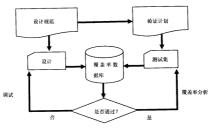

|   |   | 1.12  | 伤真      | 环境的  | 介段          |       | <br> | <br> |     |

|   |   | 1, 13 |         |      |             |       |      |      |     |

|   |   | 1, 14 |         |      |             |       |      |      |     |

|   |   | 1.15  | 565.9   | . HI |             |       |      | <br> | ,   |

|   |   |       |         |      |             |       |      |      |     |

| _     |       |       |     |         |    |    |     |    |      |      |      |    |

|-------|-------|-------|-----|---------|----|----|-----|----|------|------|------|----|

| 第 2 j |       |       |     |         |    |    |     |    |      |      |      |    |

|       | 2,1   | 内建数   | 据类  | き型・     |    |    |     |    | <br> | <br> | <br> | 19 |

|       | 2.    | 1.1 ∄ | 更解  | (logic) | 类型 |    |     |    | <br> | <br> | <br> | 19 |

|       | 2. 1  |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.2 5 |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.7   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.7   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.2   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2. 2  |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.2   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2. 2  |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.2   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.2   | 2.8 1 | 4.6 | 数组和     | 非合 | 并敷 | 组的: | 选择 | <br> | <br> | <br> | 27 |

|       | 2.3 i |       |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.5   | 关联数   |     |         |    |    |     |    |      |      |      |    |

|       |       | 连 表   |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.7   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.7   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.7   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2,7   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.8 j |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.8   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.8   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.8   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.8   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.8   |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.9 ( |       |     |         |    |    |     |    |      |      |      |    |

|       | 2.10  |       |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       | 2, 11 |       |     |         |    |    |     |    |      |      |      |    |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

|       | 2. 1  | 1.2   | 动态  | 转换      |    |    |     |    | <br> | <br> | <br> | 43 |

|       |       |       |     |         |    |    |     |    |      |      |      |    |

| -     | 33.    | vi   |

|-------|--------|------|

| ndake | 200000 | - At |

|       |        |      |

| CAST AND CORPORATE SECTIONS AND CONTRACT CONTRAC | 2000 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.11.3 流操作符                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43   |

| 2.12 枚举类型                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43   |

| 2.12.1 定义枚举值                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44   |

| 2.12.2 枚举类型的子程序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46   |

| 2.12.3 枚举类型的转换                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| 2.13 常量                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 2. 日 字符串                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 2.15 表达式的位宽                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 2,16 结束语                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50   |

| 第3章 过程语句和子程序                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 35 THE RESERVE OF THE STREET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 3.1 过程语句                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 3.2 仕方、函数以及 void 函数                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 3.3 任券和函数概述  3.3.1 在子程序中去掉 begin, , , end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| 3.3.1 在于程序中去掉 begin, , end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 3.4 于程序参数 3.4.1 C语言风格的子程序参数                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 3.4.1 C语言风格的子程序参数                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 3.4.2 参数的方向<br>3.4.3 高级的参数类型                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3.4.4 参数的缺省值                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 3.4.5 采用名字进行参数传递                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 3.4.6 常見的代码错误 3.5 子程序的返回                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3.5.1 返回(return)语句                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| 3.5.2 从函数中返回一个敷组                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 3.6 局部数据存储                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 3.6.1 自动存储                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 3.6.2 变量的初始化                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| 3.7 时间位                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3.7.2 时间参数                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| 3.7.3 时间和变量                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 3.7.4 Stime 与 Srealtime 的对比                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 3.8 结束语                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |